**UNIT-II**

Define the (i) noise immunity and (ii) Fanout. Draw the internal structure of TTL tristate gate and explain its operation.

(b) Explain the parameters used to characterize logic families. Calculate the noise margin of ECL gate.

OR

Draw the circuit for CMOS inventer. What are the different 2 schemes for CMOS to TTL interface. Explain one of them.

(b) Explain how a MOS can be used as a switch in a digital

circuit? How does a TTL gate differ from MOS gate?

**UNIT-III**

- Obtain minimum SOP expression for following Boolean 3 (a) expression using Karnaugh Map.  $F = \sum m(0,1,2,5,7,9,13,15) + d(8,11)$ Realise the minimised function using logic gates.

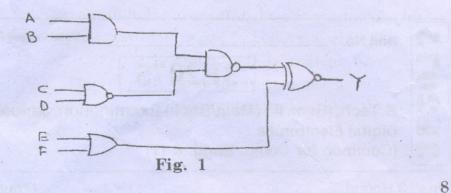

- (b) Implement the following boolean function with NOR-NOR gate logic.

Y = AC + BC + D

3 Explain briefly the systematic procedure for using don't care condition. Define multilevel logic circuit with diagram.

OR

[Contd...

8

8

8

3E20751